美媒曝刘鹤主导中国芯片逆袭计划 北京碳基芯片取得重大进展(图)

据美国财经媒体彭博新闻社6月18日报道,为发展中国半导体芯片产业,中国国家主席习近平任命69岁的国务院副总理刘鹤领导一项关键计划,以帮助中国国内芯片制造商克服美国制裁的影响。计划核心不在于追赶传统的硅基芯片,而在于弯道超车,聚焦新兴的第三代半导体芯片。彭博社的新闻标题是“芯片沙皇能保证中国成功吗?这是一个不可能实现的目标”,不看好这项中国最新芯片发展计划,但中国碳基芯片已经取得重大进展。

彭博新闻社称中国国务院副总理刘鹤为“芯片沙皇”,将负责中国第三代半导体技术发展。(中国央视新闻截图)

传统的芯片都是基于硅片制造,因而被称之为硅基芯片,与之相伴的“摩尔定律”——集成电路上可以容纳的晶体管数目每18个月增加一倍、性能提升一倍,见证了硅基芯片性能的飞速发展,但时至今日摩尔定律早已失效。从本质上来说集成电路线宽有一个无法逾越的红线,那就是一个电子的波长,线宽越接近电子波长时,电子就通过隧道效应而穿透绝缘层,使器件无法正常工作。

为提高性能突破线宽极限,即通常所说的XX纳米工艺,2011年美国英特尔公司率先将鳍式场效应晶体管(FinFET)技术引入其22纳米工艺,至今FinFEt工艺已经成为高阶半导体制程的标配,本质上FinFEt工艺类似3D堆叠技术,通过立体堆叠提高晶体管密度进而提高性能。最新的则是环绕式闸极(GAA)技术,台积电将在最新的3纳米制程种使用该技术。

但自22纳米工艺以下,至今所谓的先进制程比如台积电即将量产的3纳米制程,实际上都只是工艺代号,并不是实际的线宽即晶体管之间的距离。不同企业之间的制程也不能简单地以几纳米去区分先进与落后,晶体管密度才是唯一判断标准,比如英特尔公司的10纳米制程其晶体管密度就与台积电、三星的7纳米站在同一水平线上。

为了不断提高晶体管密度,晶体管3D堆叠技术是一条路,芯片3D封装也是一条路。原台积电首席运营官蒋尚义在台积电时就提出发展先进封装技术,意图以封装技术提高晶体管密度,蒋尚义出任中芯国际副董事长后是否会推动中芯国际走先进封装技术这条路有待观察。还有一条路那就是跳出传统的硅基芯片的窠臼,发展第三代半导体技术,利用第三代半导体材料发展全新的芯片,这就是碳基芯片。

所谓的碳基芯片是基于碳纳米管研发,碳纳米管是一种1991年被发现的新型材料,由呈六边形排列的碳原子构成的单层或者多层圆管。在制备高性能晶体管方面,它具有超高的电子和空穴迁移率、原子尺度的厚度、以及稳定的结构等优势。2009年,碳纳米管就作为未来技术选项列入国际半导体技术发展路线图(ITRS),美国IBM公司仿真结果认为平面结构碳管阵列晶体管领先硅基5个技术节点。

要实现大规模高性能集成电路,碳纳米管必须具备超高半导体纯度、顺排、高密度、大面积均匀。美国杜克大学教授Aaron Franklin 2013年在《自然》杂志上发文提出了量化的指标,即半导体纯度超过99.9999%、密度达到100至200每微米。过去20年,学界发展了多种制备、提纯、排列碳纳米管的方法,但是始终无法接近这个实用化区域。这使得碳纳米管晶体管和电路的实际性能远低于理论预期,甚至落后于相同技术节点的硅基技术至少一个量级。

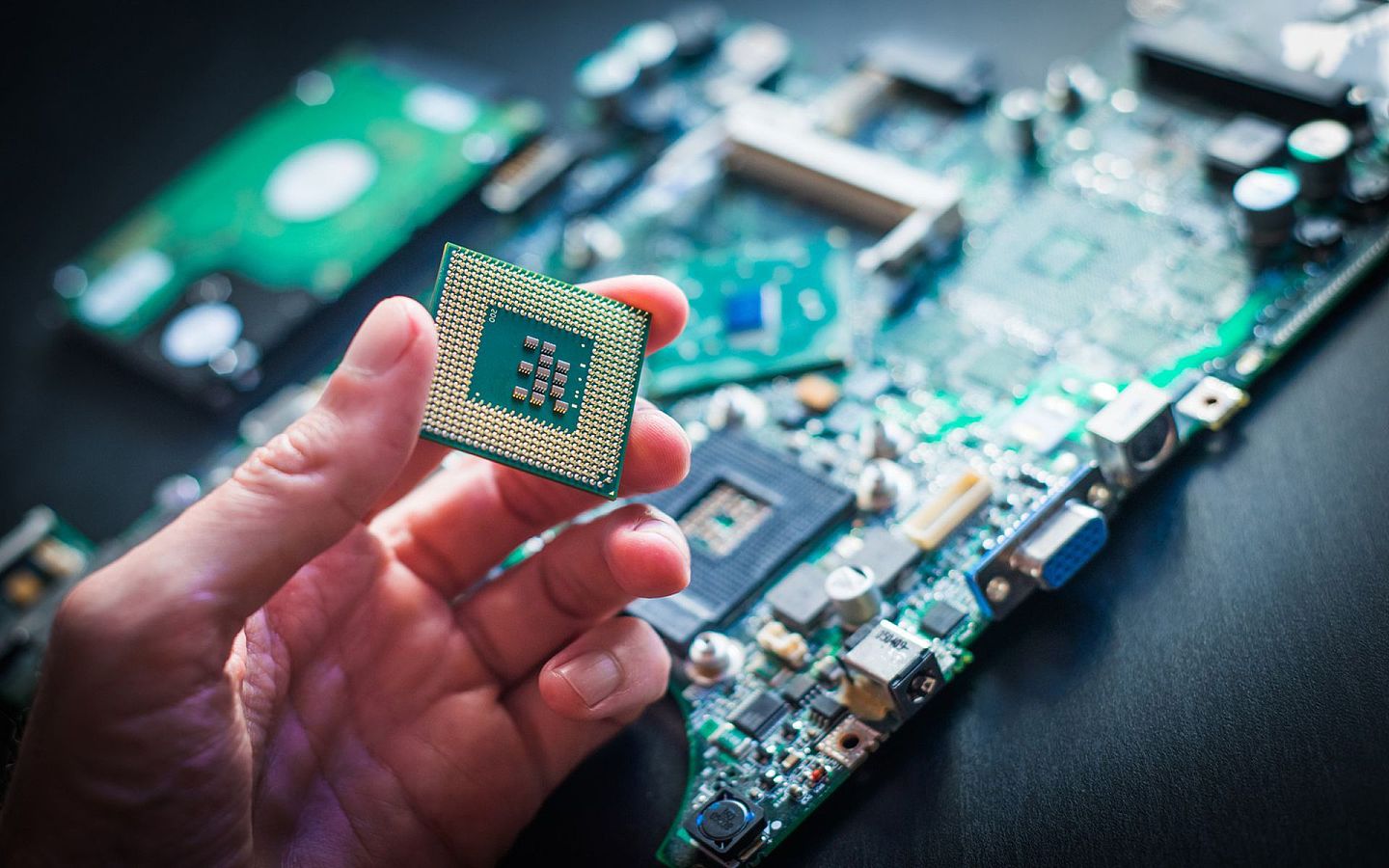

传统芯片基于硅基材料制造,美国技术上占据绝对优势,新一代碳基芯片则大家都处于同一水平线,为中国逆袭创造了条件。(视觉中国)

据北京大学信息学院电子学系主任、中国科学院院士彭练矛2020年接受媒体采访时披露,经过20年的努力由北京大学与北京市联合创建的北京元芯碳基集成电路研究院团队已经将碳纳米管半导体纯度提升到99.99995%,在4英寸晶圆上制备出了密度120每微米、直径分布1.45±0.23nm的碳纳米管阵列,理论上达到了超大规模碳纳米管集成电路的需求,并首次实现了制备出的器件和电路在真实电子学表现上超过硅基产品。下一个目标是,在未来2到3年内完成90纳米碳基CMOS先导工艺开发,性能上相当于28纳米硅基器件。“虽然不是高端技术节点,却是可以进入市场的门槛。”

北京元芯碳基集成电路研究院团队成员、北京大学信息学院教授张志勇指出,下一步的90纳米碳基CMOS先导工艺开发,面临的更多是工程性问题而原理性问题。所谓工程问题,需要大量的工程试验去解决,既需要偶然的灵光一现、神来之笔,更需要持之以恒的坚持,大量的资金投入。由副总理刘鹤负责包括碳基芯片在内的第三代半导体研发,协调各科研机构协同攻关,同时也能保证经费的持续投入,对于中国半导体产业是极大的利好。

当然,对于碳基芯片这样的显学,欧美尤其是美国绝不会错过的,前述提到的杜克大学就是美国碳基芯片研究的重镇,台积电也在联手美国斯坦福大学等研发碳纳米管,可以说全球凡是有能力的对碳基芯片都在摩拳擦掌。颠覆性技术的出现,就是一次市场洗牌的天赐良机,但愿中国能够如新能源汽车、5G、高铁等一样逆袭。

+61

+61 +86

+86 +886

+886 +852

+852 +853

+853 +64

+64